CC1100芯片数据FIFO

CC1100有2个64字节FIFO,一个用来接收数据,另一个用来发送数据。SPI接口用来读RX FIFO和写TX FIFO。FIFO控制器能侦测RX FIFO中的上溢和TX FIFO中的下溢。

当写TX FIFO时,MCU负责控制TX FIFO不产生溢出。这不会被CC1100侦测到。

同样地,当读RX FIFO时MCU必须避免读RX FIFO经过其空值,因为这会导致一个CC1100无法侦测到的错误。

当传送SPI地址时,SO脚可用的芯片状态字节包含RX FIFO的填充等级,若这个地址为读操作且TX FIFO的填充等级为写操作。

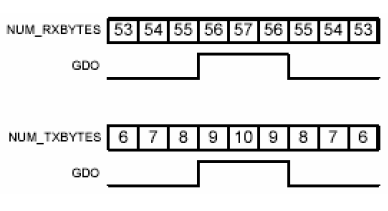

RX FIFO和TX FIFO中的字节数也能分别从状态寄存器RXBYTES.NUM_RXBYTES和TXBYTES.NUM_TXBYTES中读出来。

4位FIFOTHR.FIFO_THR设置用来控制FIFO门限点。门限值在RX FIFO和TX FIFO相反的方向上被编码。在门限值达到时,这给上溢和下溢以相等的边缘。

当FIFO中的字节数等于或大于程控门限时,会声明一个标记。这个标记用来产生FIFO状态信号,从GDO脚上可以看到。

当门限标记FIFO_THR=13时,RX FIFO和TX FIFO中的字节数。下图表示每个FIFO在门限值之上被填充满时的标记,其下是排空时对应的标记。

常规用途/测试输出控制引脚

3个数字输出引脚GDO0和GDO1和GDO2为常规控制脚。它们的功能分别由IOCFG0. GDO0_CFG 、IOCFG1.GDO1_CFG和IOCFG2.GDO3_CFG控制。下表示出了能加在GDO脚上的不同信号。这些信号能用作MCU的中断。GDO1和在SPI接口上的SO脚是同一脚,因此这个脚上控制的输出在CSn高时才有效。GDO1的默认值为3状态,当SPI接口和其它设备一起使用时这是有效的。

| GDO0_CFG[5:0]

GDO1_CFG[5:0] GDO2_CFG[5:0] |

描述 |

| 0(0x00) | 与 RX FIFO 关联:当 RX FIFO 在 RXFIFO_THR 上被填充时声明。当 RX FIFO 在

RXFIFO THR 之下时被反声明 |

| 1(0x01) | 与 RX FIFO 关联:当 RX FIFO 在 RXFIFO_THR 上被填充或到达数据包末端时声明。当

RX FIFO 空时被反声明 |

| 2(0x02) | 与 TX FIFO 关联:当 TX FIFO 在 TXFIFO_THR 上被填充时声明。当 TX FIFO 在

TXFIFO THR 之下时被反声明 |

| 3(0x03) | 与 TX FIFO 关联:当 TX FIFO 满时声明。当 TX FIFO 在 TXFIFO_THR 之下为空时被反声明 |

| 4(0x04) | 当 RX FIFO 已溢出时声明。当 FIFO 被淹没时被反声明 |

| 5(0x05) | 当 TX FIFO 已下溢时声明。当 FIFO 被淹没时被反声明 |

| 6(0x06) | 当同步词汇被送出/收到时声明,在数据包末端时反声明。对 RX,当可选地址检测失败或 RX FIFO 溢出时,引脚被反声明。若 TX FIFO 下溢,这个引脚将同样被反声明 |

| 7(0x07) | 当一个数据包被 OK CRC 收到时声明。当第一个字节从 RX FIFO 中读取时反声明 |

| 8(0x08) | 前导质量达到。当 PQI 高于控制 PQT 值时声明 |

| 9(0x09) | 清理信道评估。当 RSSI 等级低于门限时为高(决定于当前 CCA MODE 设置) |

| 10(0x0A) | 锁定检测器输出 |

| 11(0x0B) | 连续时钟。与同步连续模式下的数据同步。

数据在下降沿建立,在 SERIAL CLK 上升沿被读取。 |

| 12(0x0C) | 连续同步数据输出。同步连续模式时使用。在 SERIAL_CLK 上升沿 MCU 必须读 DO。

数据在下降沿由 CC2500 建立 |

| 13(0x0D) | 连续透明数据输出。同步连续模式时使用。 |

| 14(0x0E) | 载波感应。当 RSSI 等级低于门限时为高 |

| 15(0x0F) | CRC OK。上一个 CRC 对比匹配。当进入/重启 RX 模式时清理。 |

| 16(0x10) | 保留-测试用 |

| 17(0x11) | 保留-测试用 |

| 18(0x12) | 保留-测试用 |

| 19(0x13) | 保留-测试用 |

| 20(0x14) | 保留-测试用 |

| 21(0x15) | 保留-测试用 |

| 22(0x16) | RX_HARD_DATA[1]。能同RX_SYMBOL_TICK一起使用在交替连续RX输出上。 |

| 23(0x17) | RX_HARD_DATA[1]。能同RX_SYMBOL_TICK一起使用在交替连续RX输出上。 |

| 24(0x18) | 保留-测试用 |

| 25(0x19) | 保留-测试用 |

| 26(0x1A) | 保留-测试用 |

| 27(0x1B) | 1 时 PA PD.PA 开启,0 时功率降低。能用来控制外部 PA 或 RX/TX 开关 |

| 28(0x1C) | 1 时 LNA PD.LNA 开启,0 时功率降低。能用来控制外部 LNA 或 RX/TX 开关 |

| 29(0x1D) | RX_SYMBOL_TICK。能同RX_HARD_DATA一起使用在交替连续RX输出上。 |

| 30(0x1E) | 保留-测试用 |

| 31(0x1F) | 保留-测试用 |

| 32(0x20) | 保留-测试用 |

| 33(0x21) | 保留-测试用 |

| 34(0x22) | 保留-测试用 |

| 35(0x23) | 保留-测试用 |

| 36(0x24) | 保留-测试用 |

| 37(0x25) | 保留-测试用 |

| 38(0x26) | 保留-测试用 |

| 39(0x27) | 保留-测试用 |

| 40(0x28) | 保留-测试用 |

| 41(0x29) | CHIP RDY |

| 42(0x2A) | 保留-测试用 |

| 43(0x2B) | XOSC STABLE |

| 44(0x2C) | 保留-测试用 |

| 45(0x2D) | GDO0 Z EN N。当这个输出为 0 时,GDO0 配置为输入(为连续 TX 数据) |

| 46(0x2E) | 高阻抗(3-状态) |

| 47(0x2F) | HW 到 0(HW1 同 INV 信号一起完成) |

| 48(0x30) | CLK XOSC/1 |

| 49(0x31) | CLK XOSC/1.5 |

| 50(0x32) | CLK XOSC/2 |

| 51(0x33) | CLK XOSC/3 |

| 52(0x34) | CLK XOSC/4 |

| 53(0x35) | CLK XOSC/6 |

| 54(0x36) | CLK XOSC/8 |

| 55(0x37) | CLK XOSC/12 |

| 56(0x38) | CLK XOSC/16 |

| 57(0x39) | CLK XOSC/24 |

| 58(0x3A) | CLK XOSC/32 |

| 59(0x3B) | CLK XOSC/48 |

| 60(0x3C) | CLK XOSC/64 |

| 61(0x3D) | CLK XOSC/96 |

| 62(0x3E) | CLK XOSC/128 |

| 63(0x3F) | CLK XOSC/192 |

GOO0的默认值为125kHz-146kHz时钟输出(XOSC频率除以192)。当XOSC在重启功率下开启后,使用一个晶体,它就能用来为系统中的MCU计时。当MCU工作时,通过IOCFG0.GDO0_CFG,它能改变时钟频率。不会造成时钟波形干扰。

对IOCFG0.GDO0_CFG寄存器写入值128(0x80h),芯片内模拟温度传感器启用。然后,GDO0上的电压与温度成比例。

注:整理自网络