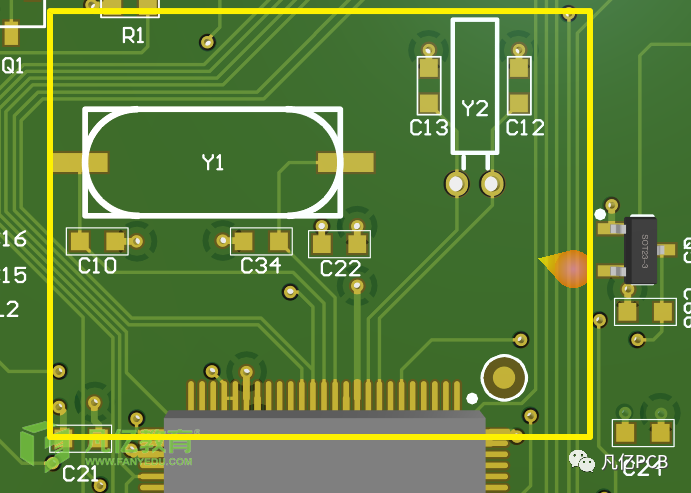

PCB设计中时钟电路晶振是非常重要的

1,引脚尽量与芯片距离近,防止受到其他信号干扰。当然也防止它干扰别的线路,因为它是信号源。

2,尽量选择铁壳晶振,其抗干扰能力强些。

3,晶振下面所有层不能走线,并铺GND铜皮。

4,晶振附近也不要有太近的数字信号线。

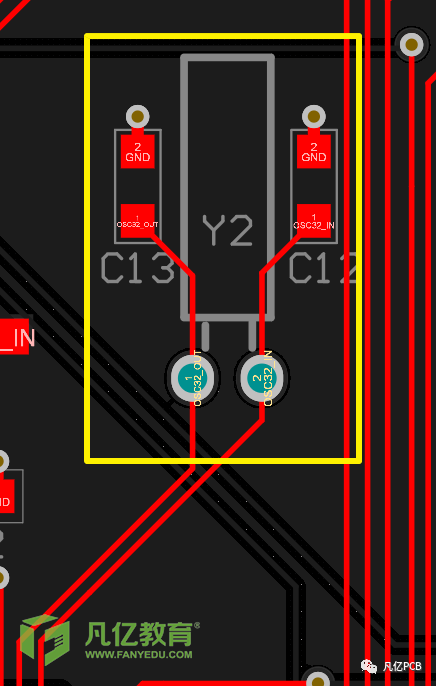

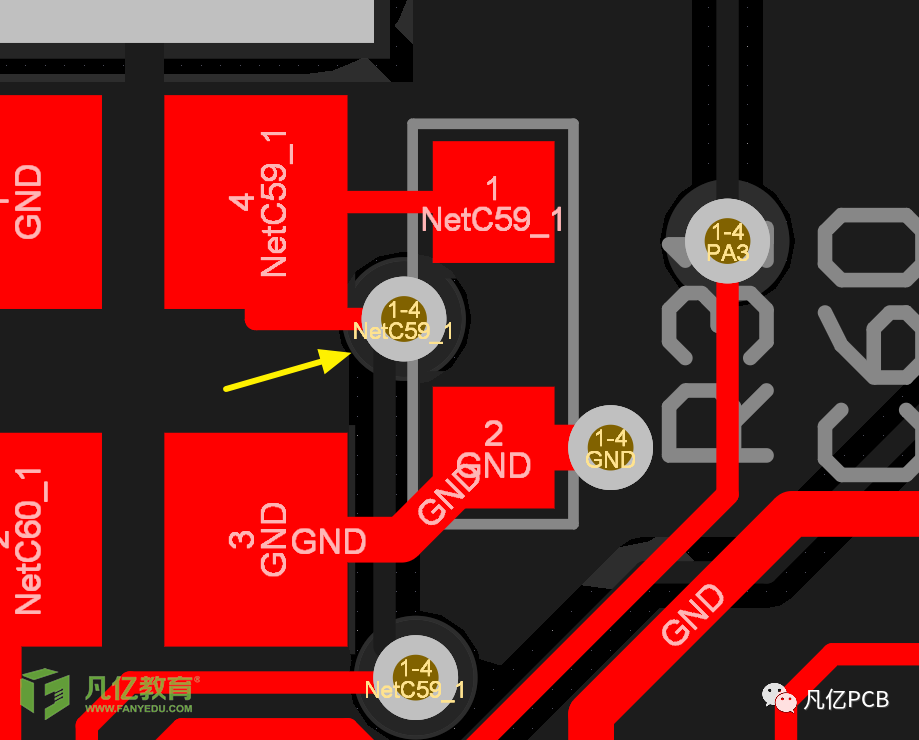

5,其负载电容的回流地一定要短。

6,对晶振进行GND包围。部分地方开窗漏GND铜,把晶振外壳焊接到开窗漏GND铜的地方。

7,布局时先经过电容后经过晶振

硬件设计布局布线注意:

1. 和 IC 布在同一层面,这样可以少打孔;

2. 布局要紧凑,电容位于晶体和 IC 之间,且靠近晶体放置,使时钟线到 IC 尽量

短;

3. 对于有测试点的情况,尽量避免 stub 或者是使 stub 尽量短;

4. 附近不要摆放大功率器件、如电源芯片、 MOS 管、电感等发热量大的器件;

5. 信号线包地处理,且包地线或者铜皮要打屏蔽地孔;

6. 晶体电路模块区域相当于模拟区域,尽量不要有其他信号穿过;

布线注意实例:

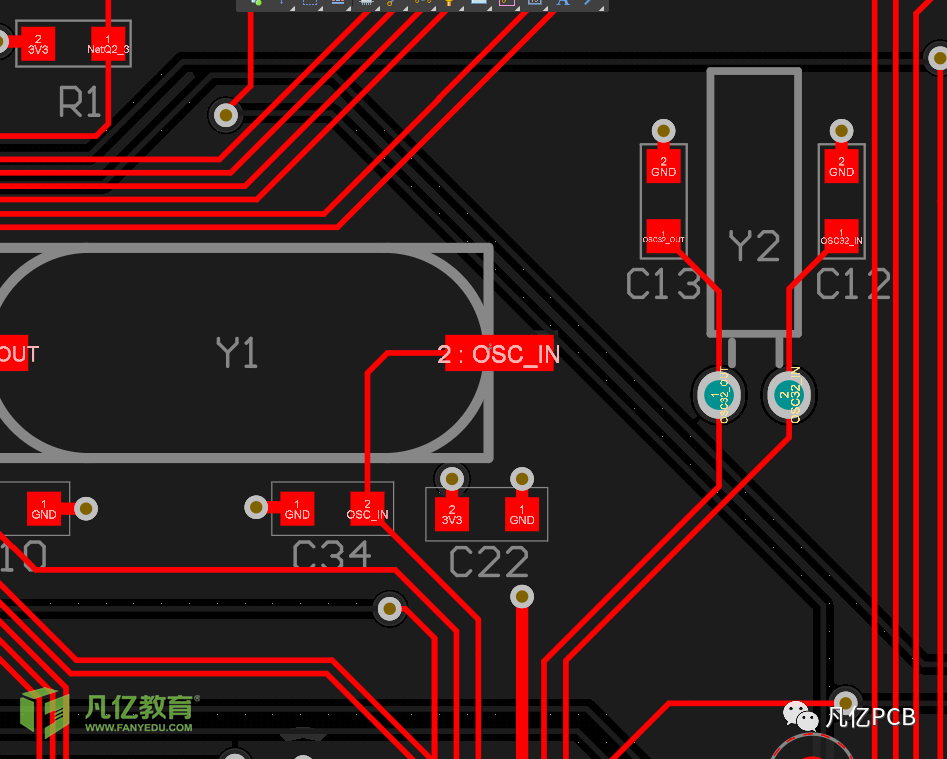

1.芯片的晶振放置得距离有点远。

【问题改善建议】:晶振相当于主芯片的心脏,优先级是最高的,所以需要靠近对应芯片的管脚放置,这个距离稍微有点远,建议后期自己手动调整下距离。

2. 晶振走线先经过的晶振再连接的滤波电容。

【问题改善建议】:建议是将信号经过滤波电容进行滤波之后,再连接的晶振,自己注意一下信号的先后性,后期去更改一下。

3. 所有的晶振都没有进行包地处理。

【问题改善建议】:晶振是需要从滤波电容的gnd出来围着晶振进行一圈的包地处理的,避免外界对于这个晶振的干扰,建议后期自己去处理一下。

4. 差分走线当做其他信号进行走线。

【问题改善建议】:建议走没一根线都应当知道其作用是什么,应该如何进行走线,此处的是一对USB的差分信号,需要创建差分和差分规则,再进行差分走线,而不是普通的信号连线。

6. 过孔打在元器件上。

【问题改善建议】:过孔不要打在丝印或者元器件上,可以将元器件挪动一下,再进行打孔。

注意:来自网络整理