EMC 设计及整改- PCB 设计原则1

布局规则

电路布局的一个原则,就是应按照信号流向的关系,尽可能做到使关键的高速信号走线最短;其次考虑电路板的整齐、美观。时钟信号尽可能短,若时钟走线无法缩短,则应在时钟线的两侧加屏蔽地线。

对于比较敏感的信号线,也应该考虑屏蔽措施。

时钟电路具有很大的对外辐射,会对一些敏感电路产生干扰,因此布局时应让时钟电路远离其它电路和电缆连接器。

低速数字I/O 电路和模拟I/O 电路应靠近连接器布放。

以下是基本要点:

(1)区域分割,不同功能种类的电路,应该位于不同区域,如对时钟电路、数字电路、模拟电路、接口电路、电源等进行分区。

(2)采用基于信号流的布局,使关键信号和高频信号的连线最短,而不是首先考虑电路板的整齐、美观。

(3)功率放大器与控制驱动部分远离屏蔽体的局部开孔。

(4)晶振,芯片的去耦电容应就近放置。

(5)基准电压源(模拟电压信号输入线、A/D 变换参考电源)要尽量远离数字信号。

器件摆放规则

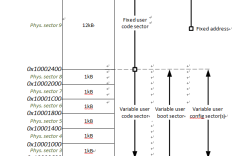

电路板上晶振是很强的辐射源,除了对晶振的电源进行滤波处理,信号走线进行控制外,在晶振外壳下方投影面积范围之内应铺大面积铜皮,为高频干扰通路提供回流路径,如下图1 所示。

PCB 单板上接口连接器很多,而且都是金属壳体,应注意金属壳体接地管脚需要接地处理,不能悬空!

布线规则

(1)地线回路原则

信号线回路构成的环路面积要尽可能小,对外的辐射越少,接收外界的干扰也越小。

(2)串扰规则

串扰是指PCB 上不同网络之间因较长的平行布线引起的互相干扰,主要是由于平行线间的分布电容和分布电感的作用。

克服串扰的主要措施有:

1)加大平行线的间距,遵循“3W”规则:为了减少线间串扰,应保证线间距足够大,当两线中心距不少于3 倍线宽时,则可保持70%的电场不互相干扰。如要达到98%的电场不互相干扰,可使用10W规则。

2)在平行线间插入接地的隔离线。

3)减少布线层与地平面的距离。

(3)走线规则

高频时钟线走线要遵循如下原则:地线护送、与数据线基本等长、在发送侧串联阻尼电阻、不走直角、手工布线。(注意:阻抗匹配十分重要,所以要根据实际情况调整阻尼电阻的值,而不是完全依据设计规则要求使用固定值。)

注: 来自于网络整理