光耦两端的数字地与模拟地如何接【EMC学习】

【现象描述】

本案例是案例"旁路电路的作用”的延续,发生在同一产品中,案例"旁路电容的作用“分析并解决了EFT/B 测试的问题,更改之后,使信号线EFT/B测试能通过±1 kV 的测试,满足了产品标准的要求,但是当进行辐射骚扰测试时,问题又出现了,辐射骚扰测试不能通过。

【原因分析】

进一步测试发现,去掉信号电缆或在电缆上套上磁环,辐射水平大大降低,说明主要与信号电缆有关,而与电缆直接相连的模拟电路部分又不是高速电路,不存在辐射测试中发现的频率及谐波相关频率。而该产品的数字电路部分有一部分是高速电路,其时钟频率为 25 MHz, 在测试频谱图中可以清楚地看到辐射较高的频点都是 25 MHz 的倍频。这样,很有可能产生辐射的噪声来自数字电路部分。

在其他的案例中已经提到过,产生辐射的必要条件是:

(1 ) 驱动源,它可以是电压源也可以是电流源。

(2) 天线。

很明显,信号电缆是产生辐射的天线,那么驱动源在哪里呢?

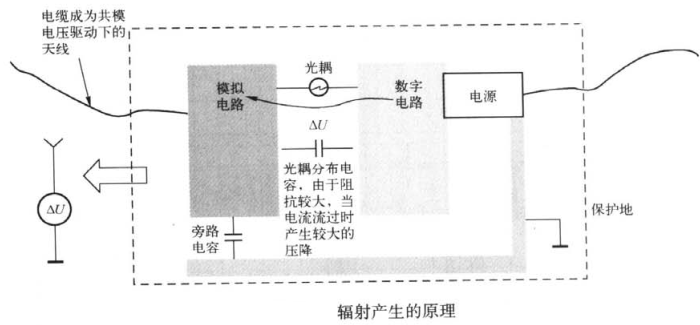

一般认为数字电路中的噪声巳经被光耦隔离了,应该不会有噪声向信号电缆方向传输,其实在高频的情况下并非如此,图1给出了辐射产生的原理。

由于光耦结电容的存在(在本案例的产品中光耦的数量5个,因此数字地与模拟地之间存在2 pFx5= 10 pF的电容), 数字电路中的部分噪声会通过光耦结电容向模拟电路方向传输。由于结电容的值并不是很大,因此电流流过时会产生较大的压降ΔU 。 该ΔU 就是驱动源,这样形成辐射的两个必要条件就产生了。

显然,降低ΔU 是本案例中辐射问题最好的解决方式。也许会有人试图通过在数字地与模拟地之间采用串联磁珠的方式来抑制噪声的传输,此方法并不能解决问题,因为磁珠是在高频下呈现高阻抗,这并不能降低ΔU。

电流流过时产生的压降与阻抗有关,按这个思路,在模拟电路的地与数字电路的地之间接旁路电容,值为1 nF, 再进行测试,测试通过。

原来,值为1 nF的电容在本案例所产生的辐射频率的范围内的阻抗要比10pF 的结电容小很多,1 nF旁路电容的连接相当于把ΔU “短路”了。这也许是个不可思议的结果,但是事实还是发生了。

经过这样改动后,也许有人会怀疑,1nF电容的存在会使EFT/B 抗干扰能力降低,理由是 1nF 电容比原来的 10pF结电容大很多,在EFT/B 干扰的频率下,阻抗也会小很多,那么自然流经数字电路的电流也会增大,因此 EFT /B 测试也许会不能通过。

经过测试,结果正好相反,抗EFT/B 干扰的能力并没有降低,相反提高了很多,原来只能 通过信号线±1kV 测试的本产品,现在能通过±2 kV 测试(拆除1nF电容后,只能通过±1kV )。

【处理措施】

按照以上的分析及测试结果,在模拟电流地与数字地之间接旁路电容,值为1nF。

提醒一点:数字电路地与模拟电路地之间接1 nF旁路电容后的确使流人数字电路的共模电流增加,这同时也是对数字电路的一种考验,本案例中之所以对整体抗扰度有所提高也是因为光耦的敏感电平相对较低。在设计时,要统筹考虑,EMC设计不仅仅是一些规则的宣贯,也要对电路特性有较深的了解。

【思考与启示】

(1 ) 相互光电隔离的数字地与模拟地之间建议采用电容连接,容值为1 nF ~ 10 nF。

(2 ) 被隔离的地之间也要考虑地电位平衡。

(3) 开关电源中变压器初级线圈与次级线圈间,跨接电容,也是基于本案例同样的原理。

注:以上用例来自《EMC电磁兼容设计与测试案例分析》