ESD 与敏感信号的电容旁路【EMC学习】

【现象描述】

某产品采用框架、PCB 插板与 PCB 背板的结构, 每一PCB 插板均有金属面板,对某一PCB插板(称VPU 板)的面板处进行 ESD 抗扰度测试时, 放电方式采用接触放电, 电压为± 4 k V , 测试时出现断话和复位现象,不能满足标准要求的ESD抗扰度测试要求。

【原因分析】

静电放电的过程伴随着辐射噪声和传导噪声,辐射噪声包括泄放电流产生的静磁场、电场和磁场。传导噪声包括直接的电荷注入及电场和磁场感应的电流。

静电放电时产生的电 磁场强度相当大。当然,在实际情况下,这些效应并不是彼此独立存在的。

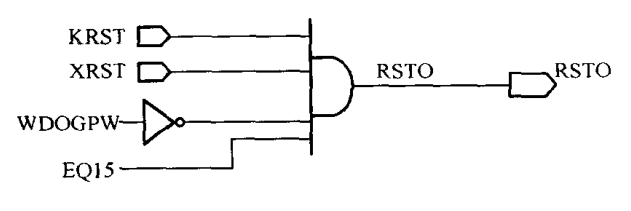

本案例中, ESD 导致 VPU板复位可能是由于该板中的控制信号线拾取到了静电放电时所产生的电磁辐射引起的,因此分析VPU 板复位的原因应从复位控制电路着手,VPU 板复位电路如图1所示。

图中KRST为手动复位键复位信号输入,XRST为来自于另一块 PCB 插板RPU 的复位信号, 当 RPU 板启动或有复位RPU 板的命令时,XRST信号会出现低电平;

WDOGPW 为看门狗复位信号; EQ15 为上电复位信号;RSTO 为复位信号输出, 送往 RPU 板主处理器。

由 VPU 板复位电路可以看出, KRST 、XRST 、WDOGPW、EQ15 4 个输入信号只要任何一个信号有效都会导致VPU 板复位。VPU 板在进行接触放电时,复位问题的定位就在于查找是哪一个复位信号在试验时受到干扰,而使VPU 板出现复位现象。

产生EQ15 上电复位信号的电路在 EPLD 内部不存在线长问题,它不应该会受到干扰引起复位,因此首先应当排除。

由于VUP 板复位电路的实现是在 EPLD 里面, 所以对其他复位信号的定位既不用割线也不用飞线 , 可以方便地通过修改EPLD 的内部逻辑来进行试验查找。

发现 KRST 复位信号线在VPU 板内部走线靠近板子的边缘, 且走线长约 12 cm, 容易受静电辐射所产生的电磁干扰影响。为了确认是否该复位信号线受到干扰导致复位,修改 EPLD 内部的复位逻辑电路,即断开复位键复位信号 KRST, 保留 RPU 板的复位信号 XRST、看门 狗复位信号WDOGPW和上电复位信号 EQ15 , 此时对上机框进行±6 kV 接触放电, VP U 板复位,初步断定并非是 KRST复位信号受到干扰而导致的复位。

怀疑静电放电时VPU 板的程序受干扰跑飞,导致看门狗复位信号有效,使 VPU板复位, 为此将 EPLD 内部的复位逻辑更改,即断开看门狗复位信号WDOGPW保留 RPU 板的复位信号XRST 、上电复位信号EQ15, 此时对上机框进行±6 kV 接触放电,VPU 板仍复位,可以断定并非是程序受到干扰而导致的复位。

此时基本可以断定是来自于RPU 板的复位信号 XRST 在静电放电时受到干扰并导致 VPU 板复位。为了验证结论, 两次修改 EPLD 内部复位控制逻辑,即在 (2) 的基础上再断开RPU 板的复位信号XRST,仅保留上电复位信号 EQ15 , 此时对面板进行±6 kV 接触放电,VP U 板不再复位,证明确实是XRST 信号受到千扰并导致单板复位。

【处理措施】

XRST 复位控制信号线从RPU 板-背板- VPU 板,走线很长,而它在进行 EPLD 输入引脚未采取任何滤波措施。在EPLD 芯片的 XRST 信号输入引脚处对VPU 板的工作地并接0.01 成的旁路电容,然后对机框进行±8 kV 接触放电测试,VPU 板不再出现复位现象。

【思考与启示】

(1) 在设计复位电路时,应考虑对复位电路进行保护,在复位信号输入引脚上并联旁路电容, 容值推荐为0 . 01 µF。

(2) 复位信号是敏感信号线,P CB 设计时应尽量减小敏感信号线的长度。

(3) 进行 ESD 问题定位对策时,由于放电过程示波器探头会拾取 ESD 放电的强辐射干扰,使得难以用示波器分清是否是信号线的干扰信号,可考虑用修改电路逻辑的方法进行分析定位。

注:以上用例来自《EMC电磁兼容设计与测试案例分析》