芯片中磁珠与去耦电容的位置【EMC学习】

【现象描述】

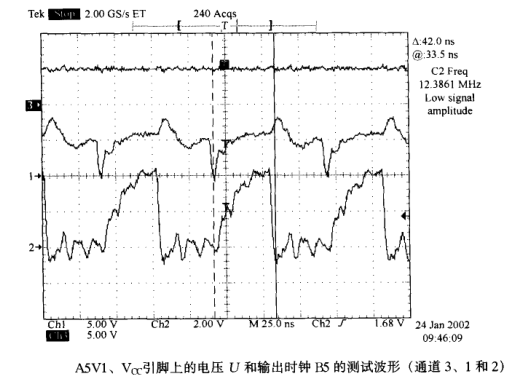

某产品PCB 板中有一时钟驱动芯片, 在供电电源 A5V1靠近时钟驱动芯片电源处并联了 10 µF的滤波电容C192 和 0.1 µF的去耦电容C202, 并经过磁珠FB5 (17010145 铁氧体—EMI磁珠-60Ω士 25% – 4. 0A – 206 ) 后, 送到芯片的 Vcc电源引脚处, 如图1所示。结果发现输出的时钟波形信号质最极差, 并且占空比也发生了变化, 进一步测试发现芯片 Vcc引脚上的电压有严重的振荡和跌落现象,振荡的频率和输出时钟的频率相同, 在 Vcc引脚上的电压跌落时,输出时钟的上升沿变得很缓,测试波形如图2所示。

【原因分析】

在PCB图中,芯片的下面是一块电源平面,在电源平面的左边和右边分别接了0.1µF的去耦电容和10 µF 的滤波电容,然后经过磁珠 FB5 送到芯片的电源引脚 Vcc, 分别是芯片的4、8、15 和 20 脚。

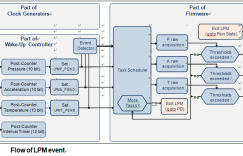

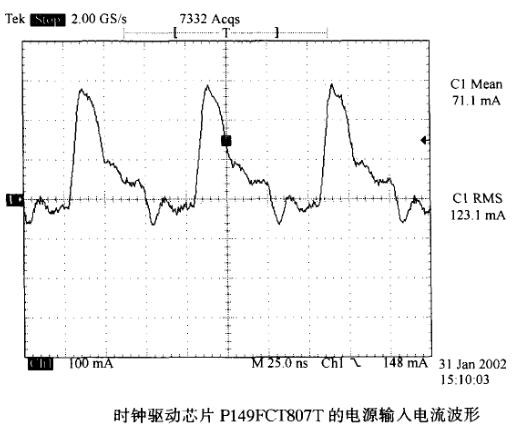

高速时钟驱动芯片的负载通常较重,在输出时钟沿跳变处,芯片电源输入电流会快速大幅度变化, 如图3所示。

时钟芯片的电源引脚Vcc先串联磁珠后并联电容, 由于磁珠的阻抗特性, 高速时钟驱动芯片电源输入电流的快速变化会在惟一的电流通路磁珠 FB5 上产生很大的反电动势,导致Vcc引脚上的电压 U 跌落和上冲。

进一步详细进行理论分析, 磁珠的电路等效可以看成是一个电感L 和一个电阻 R 的串联(有时也看成电感L和电阻R 的并联), 其中R和 L 的值都是频率的函数。

由于磁珠的电感特性,会在电源输入端产生伏特级的反电动势;又由于磁珠的阻性阻抗,叠加上-R•I 项(也是伏特级),就会导致Vcc上电压 U 很大的跌落和上冲。

【处理措施】

磁珠和电容的正确位置和连接关系是,紧靠芯片电源 Vcc引脚处直接并联10 µF 电容和 0.1 µF去耦电容,来增加抗电流跳变的能力;然后串联磁珠 FB5 与 A5Vl 平面形成高阻抗进行隔离,来减少对A5Vl 的干扰。

把两电容移到磁珠 FB5 的芯片电源侧后, 芯片工作正常, 磁珠 FB5 也达到了减少对供电电源 A5Vl 干扰的目的。

【思考与启示】

(1) 要对磁珠的原理和作用有深入的了解,认 为加个磁珠减少芯片对供电电源的干扰总没有错的想法是不正确的。

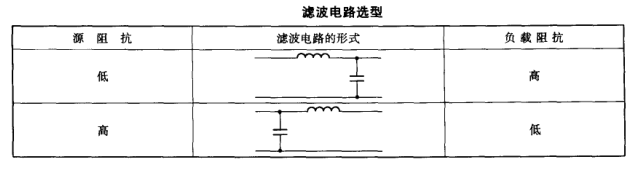

(2) 在进行滤波电路设计时一定要首先考虑源、负载的阻抗问题,滤波、去耦的原理是阻抗失配。

下表1提供滤波选型时的参考。

注:以上用例来自《EMC电磁兼容设计与测试案例分析》