局部地平面与强辐射器件【EMC学习】

【现象描述】

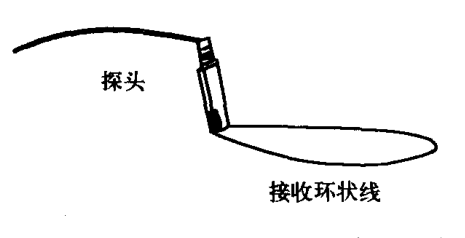

某家电产品采用塑料外壳,辐射发射超标,在问题定位过程中,用示波器及探头做成 简易的近场探头对该产品进行问题定位,示波器的具体型号及定位测试示意图如下:

测试仪器: 示波器 TDS784D (1 GHz ), 探头P6245 (1.5 GHz) 。

测试方式:把探头和探头的地线相连,形成一个环状,犹如环状接收天线,探头与地线构成的接接收环状线

收环路如下图所示,将此环靠近,寻找最大辐射点。

探头与地线构成的接收环路

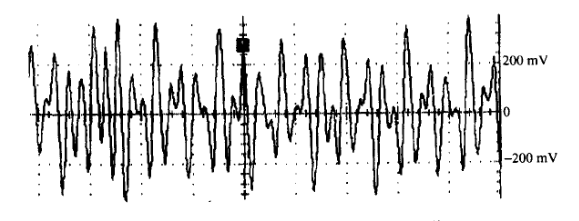

在测试中发现,当探头靠近该产品中PCB板上的晶振和其输出的时钟线时,辐射最大,探头靠近晶振时的噪声峰-峰值如下图所示,而且峰-峰值超过 400 mV。根据经验,这个幅度偏大。

因此,初步确定该时钟线或晶振在 PCB 中的设计有不合理的地方。进一步观察发现,时钟线较长, 布在 TOP 层和 BOTTOM 层, 而且该晶振的布局也没有做特殊处理。

【原因分析】

晶振及其相应的时钟信号由于其周期特性、快上升沿的特性成为 PCB 板上的主要骚扰源之一,并有着丰富的谐波。

晶体内部电路由于其特性会产生RF 电流,故封装内部产生的 RF 电流可能很大,以至于晶体的地引脚不能以很小的损耗充分地将这个很大的 Ldi/dt 电流引到地平面, 结果金属外壳变成了单极天线。PCB内的最近地平面有时离晶体外壳有两层或更多层。这样,RF 电流到地的辐射耦合路径就很不充分了。如果晶体是表贴器件,则由千表贴器件常常是塑封的,故这时的情况会变得更糟糕。封装内产生的RF 电流会辐射到空间, 耦合到其他器件,PCB材料相对于晶体地引脚具有更高的阻抗,它将阻止RF 电流进入地平面。就是这些原因使得本案例中的晶振引脚或晶振周边邻近的空间产生较大的高频噪声。

晶振、晶体和所有的应用时钟的电路(如Buffer、驱动器等,这些器件通常也具有高速、高边沿速率特性)放在一个局部地平面上是一种降低晶振、晶体等时钟电路共模辐射的一种简单而有效的方法。

局部地平面是PCB 上的一片局部敷铜,它通常在 PCB的器件(表层)面通过晶振的地引脚和至少两个过孔直接连接到PCB内部的主地平面上。除此之外,时钟驱动器、缓冲器等必须邻近振荡器放置。局部地平面应该延伸到支持逻辑电路的下面。晶振下的局部地平面实例如下图所示。

在时钟产生区域下面放置局部地平面的主要原因是:在晶体和时钟电路下面的局部地平面可以为晶体及相关电路内部产生的共模 RF 电流提供通路, 从而使 RF 发射最小。为了承受流到局部地平面的差模RF 电流,需要将局部地平面与系统中内层的其他地平面点相连。将表层局部地平面与 PCB 内部的主地平面通过低阻抗的过孔相连。有时为了提高局部地平面的性能,将时钟产生电路靠近机壳地的连接点放置,会有更好的效果。

同时应当避免有穿过局部地平面的布线,否则将破坏局部地平面的作用。如果有布线穿过局部地平面,将引起局部地平面的不连续,产生小地环路电位。在较高的频率范围内,这个地环路会带来一些问题。

【处理措施】

(1) 晶振下方表层设置局部地平面,并通过多个过孔与地层相连。

(2) 将原来布在表层的时钟线,改为布在第三层 ( 6 层板) 。

将修改后的 PCB 板安装在产品中,再用上述简易近场探头测试,测得结果峰-峰值在40 mV 左右。

【思考与启示】

(1 ) 在多层板 PCB 设计中,建议在晶振下方设置局部地平面。对于两层板, 此方法显得更为重要。

(2) 6 层以上的多层板表层或底层不允许长距离布时钟线。最大允许的表层时钟线长度为时钟信号波长的1/20。

(3) 晶振和驱动电路的下方及离这些电路300 mil的距离内不能布信号线。

注:以上用例来自《EMC电磁兼容设计与测试案例分析》