汽车电子硬件设计防电磁干扰设计学习整理4(仿真1)

实施PCB设计后,将使用3D Maxwell方程求解器(例如,高频结构仿真器(HFSS)或等效方法)提取PCB差分线的S参数,并将其与定义的频域规范进行比较 MIPI联盟D-PHY版本v1-01-00_r0-03的第7节。 如果PCB满足频域规格,则设计完成。 否则,需要改进设计。

•对于高速串行接口提取,无需在3D-EM求解器中一起提取电源和信号网。模拟仅用于信号完整性。

•使用宽带模型。建议从DC提取至少至6倍的奈奎斯特频率(对于USB3.1 Gen 1,提取模型至少至15 GHz)。

•检查电路板的堆叠,以确保准确的层厚度和材料属性。

–建议使用Djordjevic-Sarkar模型来定义介电材料。

•对堆叠中所有层上的信号走线使用精确的蚀刻轮廓和表面粗糙度。

•如果在提取之前切割了电路板布局(以减少仿真时间),请定义一个切割边界,该边界至少应与信号和电源网相距0.25英寸。

•检查通孔堆叠定义

–确保信号通孔上的非功能性内部层焊盘的建模方法与制造时相同。

– TI不建议在信号过孔上使用这些无效的内部层焊盘

•使用Spice / S参数模型(通常可从供应商处获得)对系统中的所有无源器件进行建模

需要检查提取的电路板模型的以下属性:

•无源性:这确保了电路板模型是无源网络且不会产生能量。

•因果关系:这确保董事会模型服从因果关系(输出跟随输入)。

这些检查可以在任何标准的EDA仿真器或提取引擎中执行。

一旦提取的S参数已被确认为因果和被动的,则应检查S参数图。建议检查以下内容:

•插入损耗:建议单端插入损耗保持在0到10 dB之间,最高达奈奎斯特工作频率的3倍。例如,如果目标频率为8 Gbps(4 GHz奈奎斯特),则单端插入损耗在12 GHz以下应保持在10 dB以下。

•回波损耗:建议单端回波损耗小于15 dB,最高达奈奎斯特频率的3倍。

•近端和远端串扰(FEXT / NEXT):对于高达奈奎斯特频率3倍的频率,建议FEXT和NEXT低于25 dB

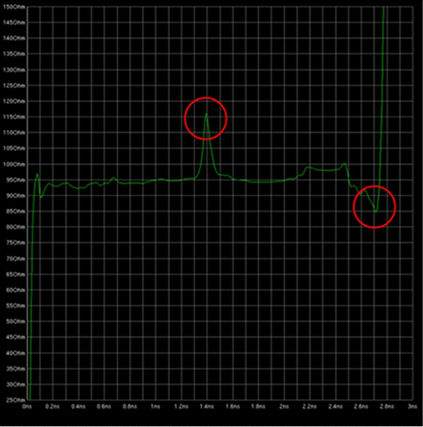

由于许多设计修复都旨在保持均匀的走线阻抗,因此,用于评估设计质量的一种重要分析方法是时域反射法(TDR)分析。 这绘制了一条迹线的阻抗随其长度的关系。 这样的一个例子如下图所示。

如上图(TDR图示例)所示,TDR图突出显示了从一端到另一端的走线中的阻抗不连续性。 此方法取决于从迹线远端反射的波形。

由于往返时间的关系,图中对应于轨迹中特定点的延迟实际上对应于该点到源的距离的2倍。 在评估阻抗不连续性的来源时需要考虑这一因素。

通过读取提取工具生成的S参数模型并在“时域”模式下对其进行评估,可以生成TDR图。 标准的EDA模拟器(例如HyperLynx)可以执行此功能。 建议将设计优化到与标称走线阻抗相差±5%之内。