汽车电子硬件设计防电磁干扰设计学习整理2

除非绝对必要,否则高速信号应在GND参考平面上布线,而不是在参考平面上的平面裂缝或空隙中布线。 不建议对电源层使用高速信号参考。

穿过平面裂缝或参考平面中的空隙的路径迫使返回的高频电流在裂缝或空隙周围流动,可能导致以下情况:

•电流不平衡导致的多余辐射

•由于串联电感增加而导致信号传播延迟的延迟

•对相邻信号的干扰

•信号完整性下降(即更多的抖动和降低的信号幅度)

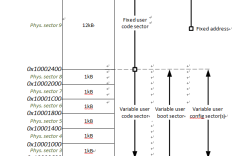

正确的平面空隙布线的示例

如果完全不可避免地要通过平面分割布线,则在分割线上跨接拼接电容器,以提供高频电流的返回路径。 这些拼接电容器可最大程度地减小电流环路面积以及因分流而产生的任何阻抗不连续性。 这些电容器应为1 µF或更低,并放置在尽可能靠近平面交叉点的位置。 正确的平面分裂布线和电容器放置的示例见下图

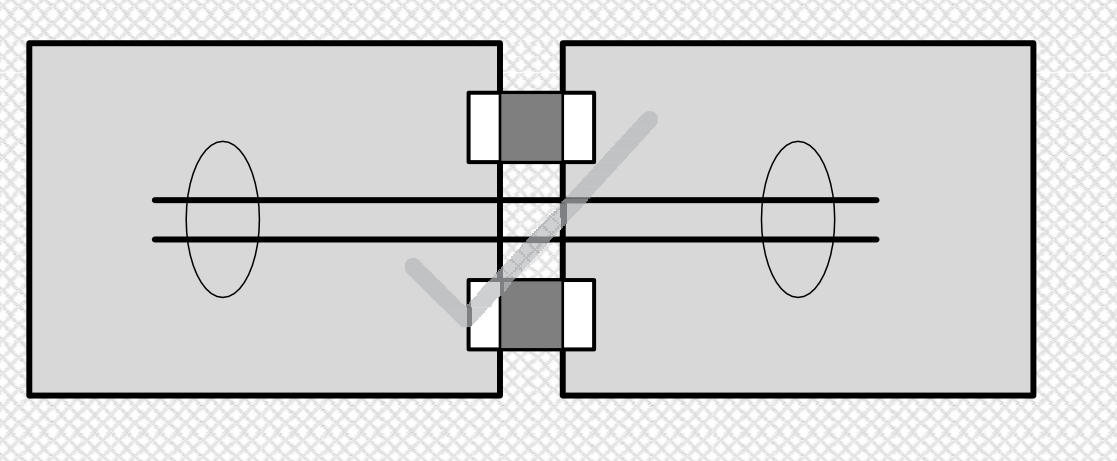

整个高速信号走线从始端到终端都应保持相同的GND参考。 如果无法保持相同的GND参考,则将两个GND平面缝在一起,以确保连续接地和均匀阻抗。 将这些缝合过孔对称地放置在信号过渡过孔的200mils内(中心到中心,越近越好)。 有关缝合过孔的示例见下图

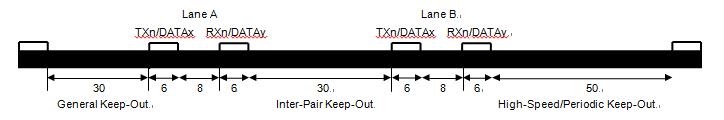

为了使高速接口实现中的串扰最小化,信号对之间的间距必须至少为走线宽度的5倍。 此间隔称为5W规则。 计算出的6mils走线宽度的PCB设计要求高速差分对之间的最小间距为30mils。 此外,在整个走线的长度上,与其他任何信号的最小保持距离都应保持30mils。 在高速差分对邻接时钟或周期性信号的地方,将此保持力增加到至少50 mils,以确保适当的隔离。 有关高速差分信号间隔的示例见下图

另外,

•请勿将探头或测试点放在任何高速差分信号上。

•请勿在使用或复制时钟信号的晶体,振荡器,时钟信号发生器,开关功率调节器,安装孔,磁性设备或IC下方或附近布线高速走线。

•在BGA突破之后,请保持高速差分信号远离SoC,因为内部状态转换过程中产生的高电流瞬变可能很难滤除。

•如有可能,将高速差分对信号在PCB的顶层或底层与相邻的GND层相连。不建议对高速差分信号进行带状线布线。(或在设计中建议对所有高速SerDes信号使用Stripline布线。这可确保更好地控制阻抗。此外,通过在接地层之间制作走线,可将EMI引起的信号质量下降降至最低)。

•确保从参考平面的边缘路由≥90mils的高速差分信号。

•确保高速差分信号的布线距离参考平面上的空隙至少1.5 W(计算出的走线宽度×1.5)。 该规则不适用于高速差分信号上的SMD焊盘无效的情况。

•SoC BGA突破后,请保持恒定的走线宽度,以避免传输线中的阻抗不匹配。

•尽可能使差分对之间的间距(松散耦合)最大化。

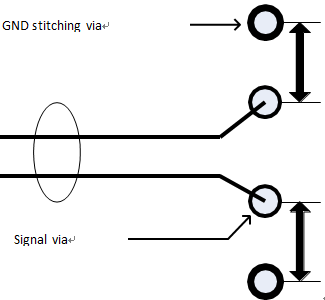

将所有高速差分对对称且相互平行地布线在一起。 在封装逃逸过程中以及在路由至连接器引脚时自然会背离此要求。 这些偏差必须尽可能短,并且包装破裂必须发生在包装的0.25英寸以内。参考下图: