TI Jacinto7 处理器的安全性优势【学】

TI 在开发 Jacinto 处理器系列的同时开发了两款灵活的高精度电源管理集成电路 (PMIC),这两款电路适用于需要功能安全的汽车应用且随附了功能安全文档。这些 PMIC(TPS6594-Q1 和 LP8764-Q1 PMIC)为主域和 MCU 域提供了可扩展的电源管理解决方案,并支持高达 ASIL-D 的功能安全。

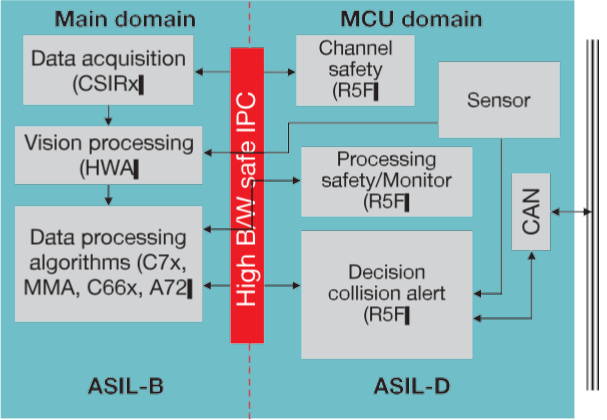

正确设计的系统可满足各种功能安全要求,包括:

SoC 检查传感器数据

MCU 检查 SoC

MCU 控制传动器

MCU 检查传动器是否以预期方式对控制做出反应

PMIC 监视 MCU 硬件和软件执行

PMIC 监视应用处理器硬件运行

如果 PMIC 检测到错误操作,那么它会强制将ENDRV 输出引脚置为低电平,从而使系统处于安全状态。

| 安全域 | 特性 | 典型汽车系统 | Jacinto 7 处理器系列优势 |

| • 架构 | • 集成 MCU Island • 异构安全内核 |

• 使用外部 MCU • 使用虚拟化管理器和外部 MCU;虚拟化需要额外的 CPU 负载 |

• 降低系统成本 • 可对安全性能进行扩展 • 无需虚拟化即可实现失效防护和恢复 |

| • 基础安全 • 瞬态和永久故障 |

• 内核、存储器和硬件加速器的 内置自检 • 存储器的错误校正码 • 锁步 DMIPS • CRC、看门狗、时钟比较器 • 互联安全 |

• 通常在应用处理器中不可用 • 针对软件诊断在所有内核上产生额外 的负载 |

• 在硬件中都可用 • 产生的额外 CPU 负载可忽略不计 |

| • 隔离 • FFI |

• MU、MPU、防火墙、超时垫圈 | • 虚拟化管理器 – 基于软件的方法 –会带来处理内核占用率 • 针对软件诊断在所有内核上产生额外 的负载 |

• 在安全任务和非安全任务之间进行硬件隔离 • 产生的额外 CPU 负载可忽略不计 |

| • 应用安全特性 | • 黑 帧 • 冻结帧 • 摄像头遮挡 • 深度学习网络参数安全 |

• 基于软件的方法 – 会带来处理内核占用率 • 针对软件诊断在所有内核上产生额外的负载 |

• 冻结帧监视器:硬件辅助冻结帧检测。无 CPU 负载 • 基 于硬件 CRC 的深度学习网络安全。无额外的 CPU 负载 |