SNP739 TPMS芯片之– I2C控制器

I2C控制器

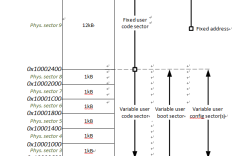

SNP739具有一个具有固定设备地址0x6C的从硬件I2C接口。当I2C被激活时,引脚GPIO0被配置为输入并用作时钟线(SCL)。引脚GPIO1也初始化为输入,用作数据线(SDA)。两条线路都需要一个上拉电阻器,可以是一个外部电阻器,也可以是通过激活内部上拉电阻器。有源设备通过将数据线拉低来传输数据。

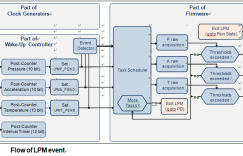

在程序模式和调试模式下,I2C接口由I2C固件管理。在这些模式下,只有某些I2C命令可用,不能执行任何应用程序代码。内部上拉电阻器由I2C处理器启用。

在正常模式下,I2C(如果需要)必须由应用程序代码管理。要激活I2C接口,必须设置位I2CEN。内部上拉电阻器自动设置为GPIO0和GPIO1。端口方向寄存器由I2C接口自动管理。

在正常模式下从主机接收数据

一旦激活,I2C寄存器将等待启动条件。以下8位被解释为设备地址,并与0x6C进行比较。如果接收到的地址匹配,则生成确认(ACK),即数据线在第9个时钟脉冲时向下拉。接下来的8位被解释为数据位,并通过将数据线拉低来确认。数据字节的完全接收由标志RXRDY指示。应用程序代码需要轮询此标志并从寄存器I2CD获取数据。RXRDY必须通过固件写入0来清除。对传入数据字节重复此过程,直到收到停止条件。如果I2C事件中断被启用,则接收器在从I2C总线接收到的每个字节上引发一个中断。

在正常模式下从SNP739向主机传输数据

设备地址的LSB用作读写指示符。因此,为了将SNP739置于数据传输模式,主机必须发送设备地址0x6D。

传输数据缓冲器用于I2C传输数据,它只支持从芯片传输两个字节的消息。必须清除传输数据缓冲区的TXRESET状态位,然后固件应将构成消息的两个字节数据写入缓冲区。传输两字节数据时,设置TXDONE位。如果I2C事件中断被启用,TXDONE中断将仅在读取两个(或更多)字节时触发,一旦触发,将不会再次发生,直到固件清除状态位TXRESET。

请注意,系统时钟应至少比I2C主时钟快2倍。

相关寄存器:

•I2CS

•I2CD

•I2CEN

注意:来自网络整理