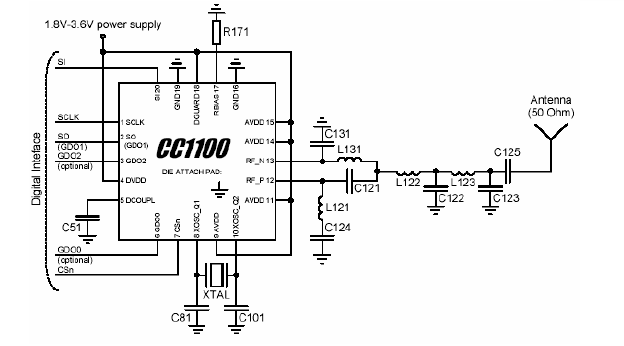

CC1100 RF收发芯片引脚结构

| 引脚编号 | 引脚名 | 引脚类型 | 描述 |

| 1 | SCLK | 数字输入 | 连续配置接口,时钟输入 |

| 2 | SO(GD01) | 数字输出 | 连续配置接口,数据输出当 CSn 为高时为可选的一般输出脚 |

| 3 | GDO2 | 数字输出 | 一般用途的数字输出脚:

测试信号 z FIFO 状态信号 时钟输出,从 XOSC 向下分割 z 连续输入 TX 数据 |

| 4 | DVDD | 功率(数字) | 数字 I/O 和数字中心电压调节器的 1.8V-3.6V 数字功率供给输出 |

| 5 | DCOUPL | 功率(数字) | 对退耦的 1.6V-2.0V 数字功率供给输出

注意:这个引脚只对 CC2500 使用。不能用来对其他设备提供供给电压 |

| 6 | GDO0

(ATEST) |

数字 I/O | 一般用途的数字输出脚:

测试信号 z FIFO 状态信号 时钟输出,从 XOSC 向下分割 z 连续输入 TX 数据 也用作原型/产品测试的模拟测试 I/O |

| 7 | CSn | 数字输入 | 连续配置接口,芯片选择 |

| 8 | XOSC_Q1 | 模拟 I/O | 晶体振荡器脚 1,或外部时钟输入 |

| 9 | AVDD | 功率(模拟) | 1.8V-3.6V 模拟功率供给连接 |

| 10 | XOSC_Q2 | 模拟 I/O | 晶体振荡器脚 |

| 11 | AVDD | 功率(模拟) | 1.8V-3.6V 模拟功率供给连接 |

| 12 | RF_P | RF I/O | 接收模式下对 LNA 的正 RF 输入信号发送模式下对 LNA 的正 RF 输出信号 |

| 13 | AVDD | RF I/O | 接收模式下对 LNA 的负 RF 输入信号发送模式下对 LNA 的负 RF 输出信号 |

| 14 | AVDD | 功率(模拟) | 1.8V-3.6V 模拟功率供给连接 |

| 15 | AVDD | 功率(模拟) | 1.8V-3.6V 模拟功率供给连接 |

| 16 | GND | 地(模拟) | 模拟接地 |

| 17 | RBIAS | 模拟 I/O | 参考电流的外部偏阻器 |

| 18 | DGUARD | 功率(数字) | 对数字噪声隔离的功率供给连接 |

| 19 | GND | 地(数字) | 数字噪声隔离的接地 |

| 20 | SI | 数字输入 | 连续配置接口,数据输入 |

CC1100用作一个低IF接收器。接收的RF信号通过低噪声放大器(LNA)放大,再对中间频率(IF)求积分来向下转换。在IF下,I/Q信号通过ADC被数字化。自动增益控制(AGC),细微频率滤波和解调位/数据包同步均数字化地工作。

CC1100的发送器部分基于RF频率的直接合成。频率合成器包含一个完整的芯片LC VCO,和一个对接收模式下的向下转换混频器产生I和Q LO信号的90度相移装置。

一块晶体将连接在XOSC_Q1和XOSC_Q2上。晶体振荡器产生合成器的参考频率,同时为数字部分和ADC提供时钟。

一个4线SPI串联接口被用作配置和数据缓冲通路。

数字基带包括频道配置支持,数据包处理及数据缓冲。

注:整理自网络