数/模混合器件数字地与模拟地如何接【EMC学习】

【现象描述】

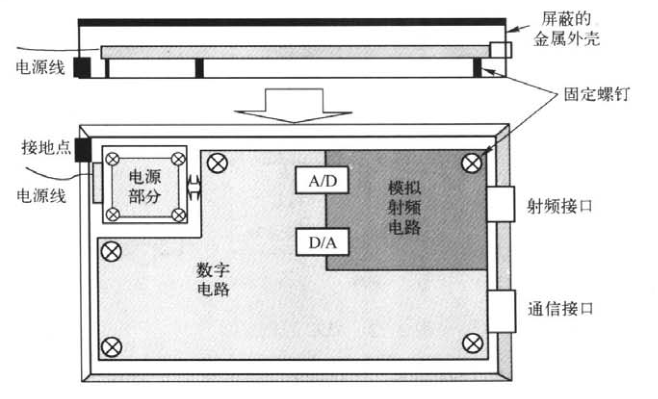

某产品是一个数字信号、射频信号混合的无线通信设备,其中数值与模拟信号之间的转换是用数恬胖专换器(DAC)和模/数转换器(ADC)来实现的。

其中的 ADC存在两种电源供电引脚,即 ADC中存在数字逻辑部分的电源和模拟逻辑部分供电的电源,与电源相对应的地也分为数字地(DGND) 和模拟地 ( AGND)。

该产品在进行6 kV 的接触静电放电试验时出现不正常工作现象,测试不能通过。后证实,测试不能通过是 ADC 不能正常工作引起的(测试中监控 ADC 的输入/输出 ,发现不一致)。

【原因分析】

该产品采用金属屏蔽结构,电源线经过滤波器之后进入产品进行供电,射频接口和通信接口均 采用金属外壳的连接器,并与机壳形成360°搭接,其中射频接口采用50Ω同轴连接器,同轴连接器外层原理上就是模拟电路的工作地即模拟地。

金属内的PCB板是数字、模拟信号混合的 PCB 板,ADC 、DAC放置在数字电路部分与模拟电路部分交界处。PCB 通过螺钉安装固定在金属外壳的底板上,并且 PCB 板中的数字电路区域的工作地(数字地)通过螺钉直接与底板相连;同样PCB板中的模拟电路区域的工作地(模拟地)也通过螺钉直接与底板相连。

静电干扰电流的放电路径主要有两条: 一条通过外壳流向大地(大部分电流);另一条通过内部 PCB板流向大地(小部分)。

静电放电电流属于高频信号, 集肤效应及金属外壳的低阻抗特性(测试中检查了金属外壳的搭接性能,确认良好,如果搭接不好也将引起额外的干扰。

既然大部分的静电放电干扰电流已经通过金属外壳流入大地,那为什么还会出现ADC 的异常工作呢? ADC 电路的设计肯定存在较薄弱的环节。

检查电路发现, ADC 存在模拟地和数字地 ,电路设计时为了使数字电路部分的干扰不影响模拟电路部分,在数字地和模拟地之间跨接了磁珠进行隔离。

由于模拟地与数字地之间存在磁珠,当高频的静电放电干扰电流流过时,会在磁珠两端产生压降ΔU。

实际上,数字电路与模拟电路之间寄生电容及磁珠的存在, 已使两部分电路相互关联, 因此ΔU的产生必然对 ADC 的正常工作产生影响 。

测试中发现,将 ADC 两边的数字地和模拟地用导线单点互连,可以通过士6 kV 的静电放电测试。

这是因为单点互连后ΔU 大大降低。

【处理措施】在模拟电路地与数字电路地之间用单点直接连接的方式。

【思考与启示】

(1)磁珠通常推荐使用在电源或信号线上来增强去耦效果,在地之间使用时一定要小心(也许某些场合可以使用),特别是有像静电放电干扰电流或EFT/B干扰电流流过时。

(2)被隔离的地之间也要考虑地电位平衡。

(3)本案例带出一个疑问,既然数字地和模拟地之间阻抗上产生的压降会出现类似本案例那样的EMC问题,那么为何不采用一种地平面的方式呢?AOC、DAC等既是模拟器件又是数字器件,那么连到哪一个接地平面更合适呢?答案是,假如把模拟地和数字地不在PCB上进行区分,模拟地的地引脚都连到数字接地平面上,那么模拟输入信号将有数字噪声叠加上去,原因是必然有一部分数字信号的回流和模拟信号的回流在地平面上重合。假如把模拟地和数字地引脚连起来并接到模拟接地平面上,会稍微好一点,原因是把几百毫伏不可靠的信号加到数字接口明显地好于把同样不可靠信号加到模拟输入端。对于10V输入的16位 AOC,其最低位信号仅为150uV。在数字地引脚上的数字地电流实际上不可能比这更坏,否则它们将使 ADC内部的模拟部分首先失效!假如在ADC 电源引脚到模拟接地平面之间接一种高质量高频陶瓷电容器 (0.1µF)来旁路高频噪声,将把这些电流隔离到集成电 路周圉非常小的范围 ,并且将其对系统其余部分的影响减到最低。虽然模拟信号也会影响数字电路,使数字噪声容限减少,但是如果低于几百亳伏,对于TTL和 CMOS逻辑通常是可以接受的。但是要注意数字信号回流平面的完整性(通常这种情况下,数字信号回流平面已经不完整了)。

(4)类似ADC、DAC的数/模混合器件,对模拟电源和数字电源要求怎么样?究竟是采用独立的模拟电源和数字电源,还是用相同的电源呢,答案是可以使用相同的电源,但是数字电源的去耦一定要做好,如在器件每个电源引脚上用0.1µF陶瓷电容适当去耦,并用一个铁氧体环把模拟电源和数字电源进一步隔离,这比地的连接更重要。

注:以上用例来自《EMC电磁兼容设计与测试案例分析》