PADS转AD过程的注意事项整理

根据PADS逻辑,单个原理图设计文件(*.SCH file)可包含多个原理图。在Altium Designer中,每个原理图都是一个单独的文件。这意味着,每个Altium Designer的原理图都对应一个文件(*.SchDoc),这是一个很大的概念区别。所有原理图文件都归集为一个项目文件(*.PrjPCB),这样可以在图与图之间建立关联。

定义网络连接性

在PADS逻辑中,网络连接性通过直接连接、网络名称字段或者power/ground/offpage符号等方式建立。

Altium Designer使用类似的网络识别符来创建关联。在一个原理图中可以使用Wires。和Net标签。在原理图表之间,网络呈扁平化设计,一般通过端口连接,OffSheet连接器也是纯粹的扁平设计。分层设计网络从一个端口的下级表连接到相同命名的Sheet Entry,它在原理图表符号中代表下级表。Power/ground网络通过Power端口连接。

PCB文件的使用

转换后的PADS布局文件将保留所有原PCB文件的电子信息:decal(封装)定义、所有走线、通路、网络名等。然而,有些区域可能需要用户检查。

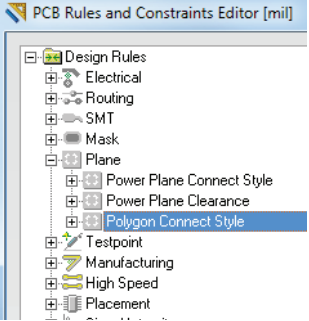

敷铜的定义与PADS稍有不同,其连接性和间距由设计规则设置,而不是由特性或参数选择决定。点击设计>>规则菜单,在“Plane”中检查 “Polygon Connect Style”规则,可查看或更改敷铜连接性。敷铜可能需要再敷以保持设计内容。

Altium Designer中的禁用区域定义也有所不同,所以需要进行检查。

设计规则中敷铜连接方式规则

当完成PADS原理图设计时,工程师会习惯于生成网络清单并将这些并不充足的信息导入到PCB工具之中。而使用 Altium Designer的过程就是进行编辑的过程。在这个过程中,工程师需要将所有可获得的信息转换到项目的统一数据库之中。而其他的域可以通过这个强大的工具箱共享这些信息。Altium Designer通过ECO(engineering

change order,工程变更指令)来实现数据在域之间的传递。利用ECO,工程师可以完全掌控传输内容。

当点击Project>>Compile Project时,编辑过程将建立项目source原理图(或HDL)文档之间的结构关系,然后决定各表内的网络等级连接性,最后确定各表之间的连接性。

所有设计原理图的元件和链接信息都应写入Altium Designer的统一内部数据库结构之中,而这些信息都可用于众多的post-compilation活动之中,如,比较原理图之间的差异、参数管理、参数导航间的差异、原理图和PCB间的交叉询查等等。