电源布局和退耦

低阻抗地面的可靠性确定之后,PCB设计的下一步是电源布线。

(1) 电源面与电源走线

在多层PCB设计过程中,一个方法是完整的面作为电源面,另一个设计方法包括电源走线或者结合两种技术。最优方案是把两者优点相结合,因此应该采用本地电源面并且通过迹线连接到供电系统上,不同的供电系统应设在同一层或通过地面分离以减少这些供电系统之间的串扰,虽然本地电源面易于操作,但当连接电源引脚和腿耦电容到平面上时,应该特别谨慎。

(a) 退耦电容的连接

微控制器最关键的引脚去耦,往往是在PCB 设计过程中最苛刻的一部分,即使是在一个多层设计中,每毫米迹线都要仔细考虑。

(b) 拟定等效电路

当考虑到最佳位置,方向和电容的连接时,纸和铅笔仍然是有益的工具,画一个草图可能会非常有用。每一条线应拟阻抗画出,即使实际意义并不大。

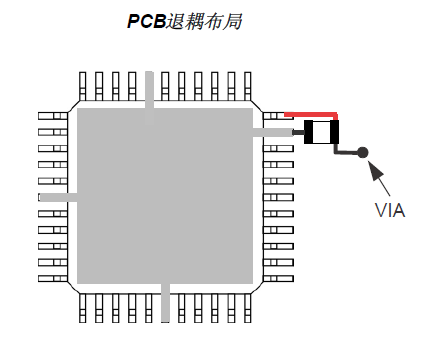

下图1展示了PCB 的布局,连接到本地地面的线应尽可能短,电源线从本地器件通过电容焊盘再经过一个VIA (通孔连接)连接到内部电源面。

例如,把过孔放在该红色痕迹中心,会添加几个nH 电感到电容阻抗,从而将大大地降低滤波效率。此外,其他引脚和/或装置的电源线必须不能从红色痕迹引出,因为它会引起很大的躁声。

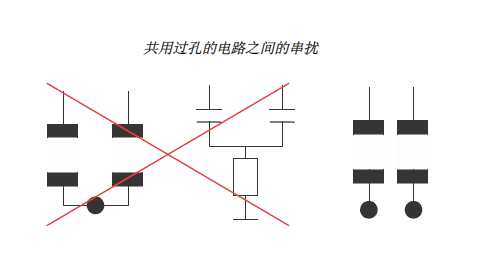

(2) 过孔有相当大的阻抗

任何痕迹和过孔都有一个相当大的阻抗,因此关键电路的过孔如去耦电路必须是独立的电路,下图2左边2 个图说明了一个共同原因,相关联电路之间共用一个过孔会引起串扰,最右边图展示的是正确接线。

(3) 滤波器

如果按照上述设计技术,那么大多数应用都能够完成EMC 要求,不过,有关键EMC 要求的或复杂的设计,可能需要再加滤波元件,根据NEC EE 经验,应该利用一个多级的电源滤波器。

(a) 多级电源滤波器

最关键的电源应利用多级滤波以实现最大可能的噪声抑制。下图是滤波电路的例子,如前所述每一条线的阻抗都应已予考虑,尤其是垂直元件的连接(例如:所有电容)是至关重要的,例如T型过滤器提供一个完美的电源线与电容的连接并且没有增加额外的阻抗。只有PCB设计提供了一个到地面的相对较低阻抗,全面躁声抑制才能实现。见下图3所示。

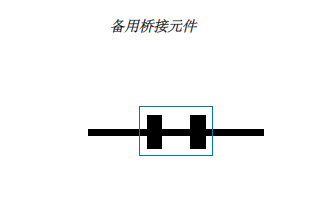

(b) 备用桥接元件

当电源电压失真时,最佳的滤波措施是根据评估结果删减可能并不需要的部分,并行元件较易删减,但串行元件需要根据情况选择桥接元件, 如下图4 所示,如果实验证明了串行元件的必要性,所有部分其他元件都将移走,以至为新元件提供空间,另一方面, 不要提供太多的额外元件,因为这些可能造成空间的限制,影响其他部分的电路。

注; 整理自网络